漏极开路是什么意思?漏极开路输出/输出及其原理介绍

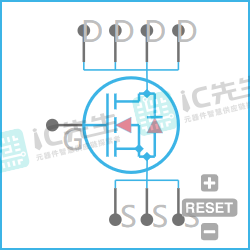

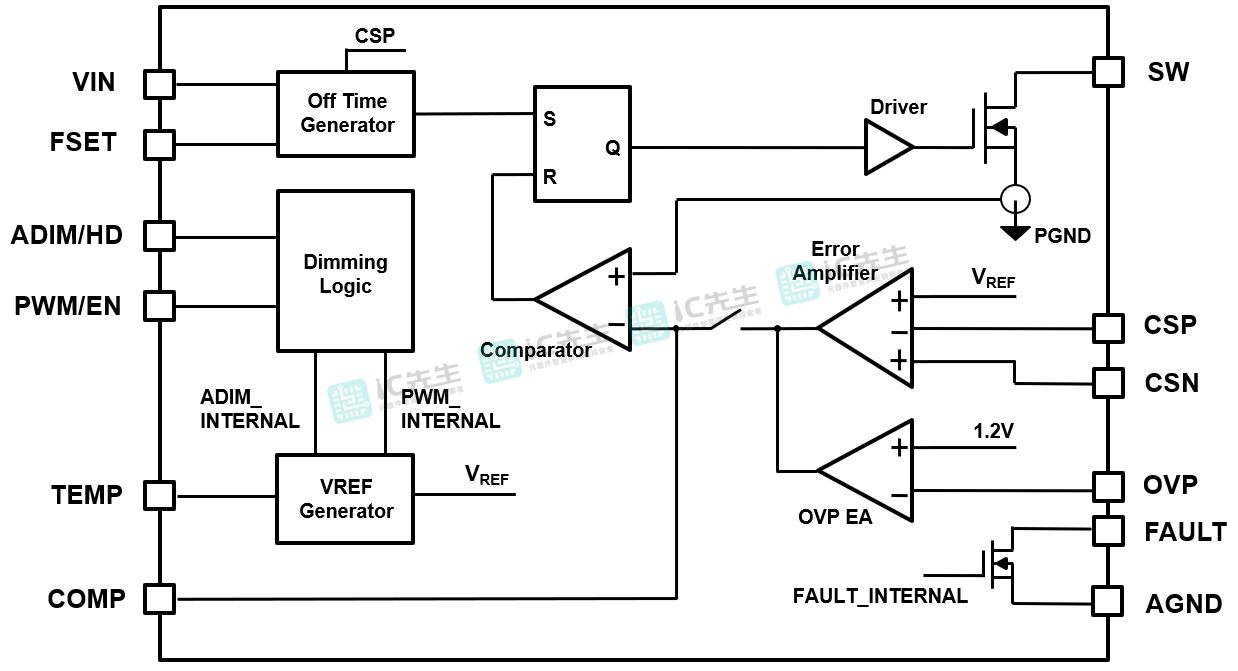

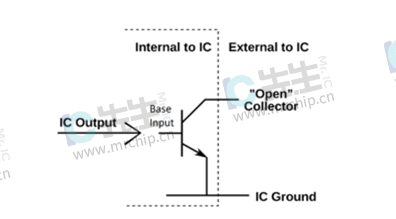

漏极开路或者集电极开路输出引脚只是一个接地的晶体管,每当在栅极上施加高输入时,漏极和源极就会短路。每当在栅极上施加低输入时,漏极和源极就会断开连接。

所以为简单起见,漏极开路就像一个开关,它会根据给定的输入信号进行连接或断开连接。在本文中,将简单介绍漏极开路的电路及其工作原理等内容。

输入/输出配置

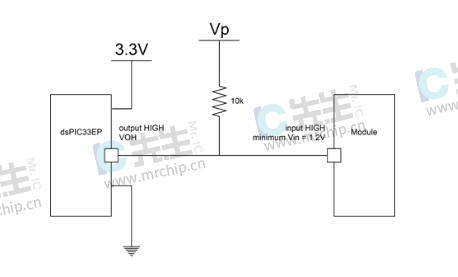

漏极开路常见于许多集成电路中,这有助于多个设备使用处于下拉操作模式的单线连接。这根单线也是双向的,因此由于许多设备在一条公共线上互连,因此它的双向特性将对电路变得非常重要。

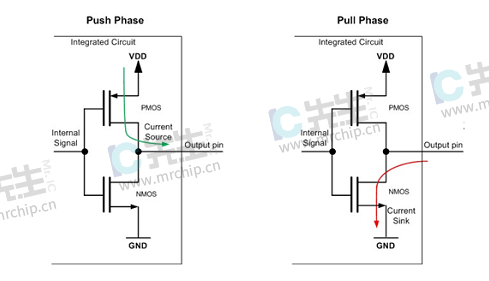

在配置方面,漏极开路具有带推挽的可编程输出配置。数字输出的操作有两种模式,一种是推挽模式,另一种是漏极开路模式。

在漏极开路模式下进行操作时,较高的晶体管将被禁用,0继续接地,输出1将断开到Vio的引脚并保持浮动。当在推挽模式下完成配置时,0将输出引脚接地,1将连接到Vio。下面是漏极开路和推挽模式的比较:

开关

- 推挽将包含两个开关,一个开关接地,另一个开关连接到Vcc。

- 漏极开路仅由一个接地的开关组成。

输出

- 在推挽模式中,如果输出引脚变高,则引脚通过开关接地。当输出引脚变为低电平时,该引脚将随着开关关闭而开始浮动。

- 在漏极开路模式中,如果输出为高引脚,则通过NPN开关连接到Vdd。如果输出为低电平,则该引脚将在PNP开关的帮助下接地。

能量消耗

- 推挽功耗非常低,因为它不需要任何上拉电阻。

- 由于在开启时通过负载电阻漏电,因此漏极开路需要高功耗。

运行速度

- 与推挽模式相比,漏极开路的开关速度较慢。

- 推挽模式运行速度快。

负载

- 推挽模式不会驱动外部负载。

- 漏极开路模式将直接驱动小于或等于10ma的外部负载。

信号

- 推挽无法将各种传感器的Vout信号组合到公共总线上。

- 漏极开路能够切换高于或低于Vdd电源电压的电压。

另外,在漏极开路与集电极开路中,漏极开路是CMOS,集电极开路是BJT。当电流较低时,BJT的饱和电压略高于FET的RDS引起的压降。

漏极开路GPIO

- PMOS在漏极开路配置中不存在,输出有高电平或悬空两种可能性。

- NMOS将通过在输出数据寄存器中提供0来激活,并且I/O引脚接地。

- 当给定且I/O状态未定义时,输出数据寄存器将使端口处于Hi-Z。

- 要解决此问题,必须激活内部上拉电阻或另一个提供外部上拉电阻。当上拉电阻被激活时,I/O引脚将其状态变为Vdd。

漏极开路配置的输出模式只不过是顶部的PMOS晶体管根本不存在。当晶体管关闭时,漏极将打开,因此输出将浮动。开漏输出配置不能上拉引脚只能下拉引脚。GPIO的开漏输出配置是无用的,除非它具有上拉能力:

所以,要在实际应用中使用它,它必须与外部上拉电阻或内部上拉电阻一起使用。在目前的情况下,所有MCU都支持每个GPIO引脚的内部上拉电阻,但必须使用GPIO配置来激活或停用它们

如何驱动LED

为了首先能够驱动LED,在将LED连接到引脚后激活内部上拉电阻。要打开LED,只需将1作为输入,这样它就会反转为0,晶体管将关闭。当它关闭时,上拉电阻将帮助LED被驱动至Vcc。同样,如果想关闭LED,只需将0输入即可,这样晶体管就会导通,从而使 LED 关闭。

需要注意的是,内部上拉电阻的值是固定的,其范围从10千欧到250千欧,完全可以满足实际应用程序的运行。

在漏极开路MOSFET中,MOSFET就像一个晶体管,能够处理更高的电压。晶体管的开关行为由基极控制。当IC输出流向基极时,如果流过IC输出的电流很少,电流将通过晶体管开启,同样,电流将不会流过晶体管。晶体管通过基于IC的数十亿晶体管制成的电路控制电流和电压电位的流动。

当NPN晶体管打开但连接到外部引脚时,它是一个集电极开路,这将使晶体管在激活时切换到地。这趋向于电流吸收器和电流源获得电流,但方向不同。

在漏极开路 I²C中,无论何时使用 I²C,串行时钟引脚和串行数据引脚都将处于其配置中。为了使总线正常工作,必须在内部或外部为每个引脚连接上拉电阻。I²C总线中上拉电阻的正确值取决于总线的总电容和总线工作的频率。但是可以通过考虑I²C总线速度电容等来计算上拉电阻的值,但电阻值范围为4.7千欧到10千欧有效。

总结

漏极开路通常应用于场效应管(FET)的保护电路中。在正常操作中,场效应管的漏极通常与负极连接。如果漏极开路,会导致场效应管不再导电,从而保护电路免受电流过载或短路的损害。此外,漏极开路也可用于信号调节电路中,以控制电路的输出信号。