DAC12DL3200产品规格_功能图_原装供应

IC先生 网络 88 2023-11-15 08:16:00

DAC12DL3200 是一款延迟非常低的双通道射频采样数模转换器 (DAC),输入和输出速率在双通道模式下高达 3.2GSPS,或在单通道模式下高达 6.4GSPS。当使用多种奈奎斯特输出模式时,DAC 可以在接近 8GHz 的载波频率下传输超过 2GHz 的信号带宽。高输出频率范围支持在 C 频带 (8GHz) 及以上的带宽下直接采样。

DAC12DL3200 可用作双通道模式下的 I/Q 基带 DAC。高采样率和输出频率范围还使 DAC12DL3200 能够支持任意波形生成和直接数字合成 (DDS)。集成 DDS 块可在片上实现单音和双音生成。

DAC12DL3200 具有并行 LVDS 接口,该接口包含多达 48 个 LVDS 对和 4 个 DDR LVDS 时钟。选通信号用于同步可通过最低有效位 (LSB) 或专用选通 LVDS 通道发送的接口。每个 LVDS 对可高达 1.6Gbps。使用同步信号 (SYSREF) 支持多器件同步,多器件同步与 JESD204B/C 时钟器件兼容。SYSREF 窗口化简化了多器件系统中的同步。

DAC12DL3200的特性

- 12 位分辨率

- 最大输入和输出采样率:

- 单通道采样率高达 6.4GSPS

- 双通道采样率高达 3.2GSPS

- 多奈奎斯特工作模式:

- 单通道模式:NRZ、RTZ、RF

- 双通道模式:NRZ、RTZ、RF、2xRF

- 通过器件的延迟较低:6ns 至 8ns

- 为低延迟接收器 ADC12DL3200 提供合适的发送功能

- DAC 和 ADC 总延迟 < 15ns(不包括 FPGA)

- 并行 DDR LVDS 接口:

- 源同步接口可简化时序:

- 24 或 48 个速率高达 1.6Gbps 的 LVDS 对

- 每个 12 位总线有 1 个 LVDS DDR 时钟

- 输出频率范围:> 8GHz

- 满量程电流:21mA

- 简化时钟和同步

- SYSREF 窗口化可简化设置和保持时间

- 片上直接数字合成器 (DDS)

- 单音和双音正弦波生成

- 32 x 32 位数控振荡器

- 快速跳频功能 (< 500ns)

- 同步 CMOS 频率/相位输入

- fOUT = 4.703GHz、6.4GSPS、射频模式下的性能

- 输出功率:-3dBm

- 本底噪声(70MHz 偏移):-147dBc/Hz

- SFDR:60dBc

- 电源:1.0V、1.8V、–1.8V

- 功耗:1.49W(双通道、射频模式、3.2GSPS)

- 封装:256 焊球 FCBGA(17x17mm,1mm 间距)

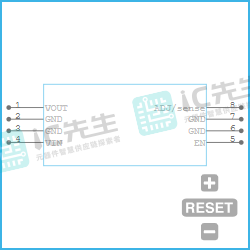

DAC12DL3200功能图

DAC12DL3200规格参数

| 产品属性 | 属性值 |

|---|---|

| 决议(位) | 12 |

| DAC通道数 | 1, 2 |

| 接口类型 | DDR LVDS, Parallel LVDS |

| 采样/更新率(Msps) | 3200, 6400 |

| 特性 | Ultra High Speed |

| 评级 | Catalog |

| 插值 | 1x |

| 功耗(型)(mW) | 1400 |

| SFDR (dB) | 80 |

| 体系结构 | Current Source |

| 工作温度范围(℃) | -40 to 85 |

| 引用类型 | Ext, Int |

周度热榜

月度热榜

年度热榜

版权声明:

部分文章信息来源于网络以及网友投稿,本网站只负责对文章进行整理、排版、编辑,是出于传递更多信息之目的,并不意味着赞同其观点或证实其内容的真实性,如本站文章和转稿涉及版权等问题,请作者及时联系本站,我们会尽快处理。

文章标签:

芯片