LMK04228产品规格_功能图_原装销售

IC先生 网络 107 2023-11-18 13:30:07

LMK04228 器件是支持 JEDEC JESD204B 且在业界具有高性能的时钟调节器。

PLL2 可以配置 14 个时钟输出以驱动 7 个 JESD204B 转换器或其他逻辑器件(使用器件和 SYSREF 时钟)。SYSREF 可以通过直流和交流耦合提供。不只是 JESD204B 应用,14 个输出中的每一个输出都可以单独配置为用于传统时钟系统的高性能输出。

LMK04228 既具有出色的性能, 又具有 多种特性,如功率和性能均衡调节、双 VCO、保持模式和可根据输出调节的模拟和数字延迟,是提供灵活的高性能时钟树的理想器件。

LMK04228的特性

- JEDEC JESD204B 支持

- 超低 RMS 抖动

- 156fs RMS 抖动(12kHz 至 20MHz)

- 245fs RMS 抖动(100Hz 至 20MHz)

- 245.76MHz 时具有 –162.5dBc/Hz 本底噪声

- PLL2 提供多达 14 个差动器件时钟

- 多达 7 个 SYSREF 时钟

- 最高时钟输出频率:1.25GHz

- PLL2 提供 LVPECL、LVDS 可编程输出

- PLL1 提供缓冲的 VCXO 或晶体输出

- LVPECL、LVDS、2xLVCMOS 可编程输出

- 双环路 PLLatinum™锁相环 (PLL) 架构

- PLL1

- 多达 3 个冗余输入时钟

- 自动和手动切换模式

- 无中断切换和 LOS

- 集成低噪声晶体振荡器电路

- 输入时钟丢失时采用保持模式

- 多达 3 个冗余输入时钟

- PLL2

- 标准 [1Hz] PLL 本底噪声为 -224dBc/Hz

- 相位检测器频率高达 155MHz

- OSCin 倍频器

- 两个集成低噪声 VCO

- 标准 [1Hz] PLL 本底噪声为 -224dBc/Hz

- 50% 占空比输出分配,1 至 32

(偶数和奇数) - 精密数字延迟

- 25ps 步长模拟延迟

- 多模式:双 PLL 或单 PLL

- 工业温度范围:–40°C 至 85°C

- 3.15V 至 3.45V 工作电压

- 封装:64 引脚 WQFN (9.0 × 9.0 × 0.8mm)

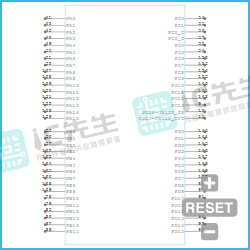

LMK04228功能图

LMK04228规格参数

| 产品属性 | 属性值 |

|---|---|

| 函数 | Dual-loop PLL |

| 输出数量 | 15 |

| 有效值抖动(fs) | 156 |

| 输出频率(min) (MHz) | 0.315 |

| 输出频率(最大)(MHz) | 1250 |

| 输入类型 | LVCMOS, LVDS, LVPECL |

| 输出类型 | LVCMOS, LVDS, LVPECL |

| 电源电压(min) (V) | 3.15 |

| 电源电压(最大)(V) | 3.45 |

| 特性 | JESD204B |

| 评级 | Catalog |

| 工作温度范围(℃) | -40 to 85 |

| 输入通道数 | 3 |

版权声明:

部分文章信息来源于网络以及网友投稿,本网站只负责对文章进行整理、排版、编辑,是出于传递更多信息之目的,并不意味着赞同其观点或证实其内容的真实性,如本站文章和转稿涉及版权等问题,请作者及时联系本站,我们会尽快处理。

文章标签:

芯片