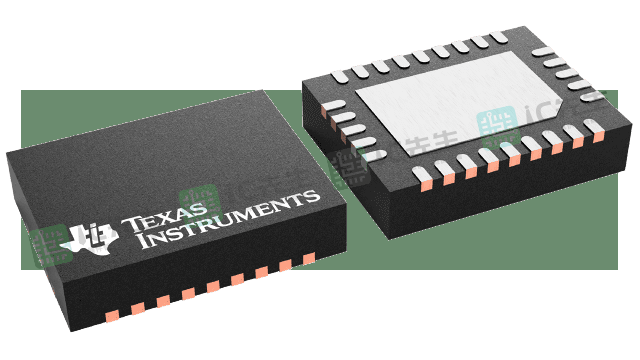

LMK04826产品规格_功能图_现货出售

IC先生 网络 78 2023-11-18 17:34:02

LMK0482x系列是业界性能最高的时钟调节器,支持JEDEC JESD204B。

PLL2的14个时钟输出可以配置为驱动7个JESD204B转换器或其他逻辑器件,使用器件和SYSREF时钟。SYSREF可以使用直流和交流耦合来提供。不仅限于JESD204B应用程序,14个输出中的每一个都可以单独配置为传统时钟系统的高性能输出。

LMK0482x系列的高性能,加上在功率或性能、双vco、动态数字延迟、延迟和无故障模拟延迟之间进行权衡的能力,使其成为提供灵活的高性能时钟树的理想选择。

LMK04826的特性

- JEDEC JESD204B支持

- 超低有效值抖动

- 88fs RMS抖动(12 kHz至20 MHz)

- 91 fs RMS抖动(100hz至20mhz)

- –162.5 dBc/Hz Noise Floor at 245.76 MHz

- 多达14个差动器件时钟从PLL2

- 最多7个SYSREF时钟

- 最大时钟输出频率3.1 GHz

- LVPECL, LVDS, HSDS, LCPECL可编程输出从PLL2

- 最多1个缓冲VCXO/晶体输出从PLL1

- LVPECL, LVDS, 2xLVCMOS可编程

- Dual Loop PLLatinum™ PLL Architecture

- PLL1

- 多达3个冗余输入时钟

- 自动和手动切换模式

- 无命中切换和LOS

- 集成低噪声晶体振荡器电路

- 输入时钟丢失时的保持模式

- 多达3个冗余输入时钟

- PLL2

- 归一化[1hz]锁相环底噪声

–227 dBc/Hz - 相位检测器速率高达155 MHz

- OSCin Frequency-Doubler

- 两个集成的低噪声vco

- 归一化[1hz]锁相环底噪声

- 50%占空比输出分,1 ~ 32

(偶数和奇数) - 精密数字延迟,动态可调

- 25ps步进模拟延迟

- 多模式:双锁相环、单锁相环和时钟分布

- Industrial Temperature Range: –40 to 85°C

- Supports 105°C PCB Temperature (Measured at Thermal Pad)

- 3.15 v至3.45 v运行

- Package: 64-Pin QFN (9.0 mm × 9.0 mm × 0.8 mm)

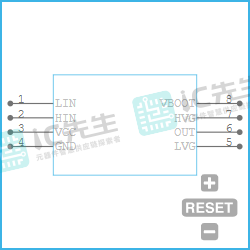

LMK04826功能图

LMK04826规格参数

| 产品属性 | 属性值 |

|---|---|

| 函数 | Dual-loop PLL |

| 输出数量 | 15 |

| 有效值抖动(fs) | 88 |

| 输出频率(min) (MHz) | 0.225 |

| 输出频率(最大)(MHz) | 2505 |

| 输入类型 | LVCMOS, LVDS, LVPECL |

| 输出类型 | LVCMOS, LVDS, LVPECL |

| 电源电压(min) (V) | 3.15 |

| 电源电压(最大)(V) | 3.45 |

| 特性 | JESD204B |

| 评级 | Catalog |

| 工作温度范围(℃) | -40 to 85 |

| 输入通道数 | 3 |

周度热榜

月度热榜

年度热榜

版权声明:

部分文章信息来源于网络以及网友投稿,本网站只负责对文章进行整理、排版、编辑,是出于传递更多信息之目的,并不意味着赞同其观点或证实其内容的真实性,如本站文章和转稿涉及版权等问题,请作者及时联系本站,我们会尽快处理。

文章标签:

芯片