SN74AUP1G34DRLR缓冲器驱动器引脚参数功能描述

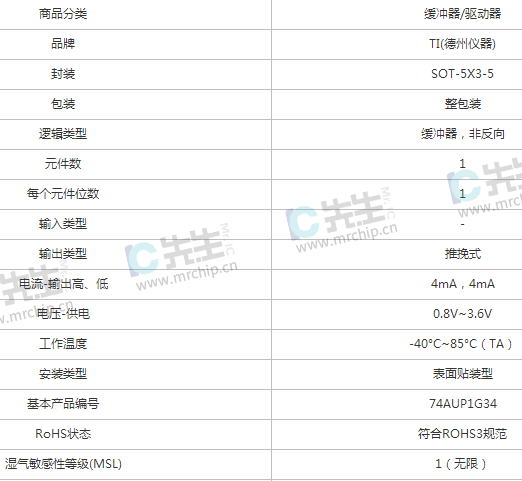

SN74AUP1G34DRLR型号元器件是一款缓冲器、驱动器,该单个缓冲门在0.8V至3.6V之间工作,并在正逻辑中执行布尔函数Y=A,AUP系列设备的静态功耗小于1µA,属于超小型DPW包裹DPW封装技术是IC封装的重大突破,下面来看看SN74AUP1G34DRLR型号驱动器的产品规格参数等信息。

它的0.64毫米见方占地面积比其他封装选项节省了大量的电路板空间,同时仍保留了传统的制造友好的引线间距为0.5mm,此设备完全指定用于使用Ioff的部分断电应用,Ioff电路禁用输出,防止在设备通电时损坏电流回流通过设备,Ioff功能还允许实时插入。

产品图片

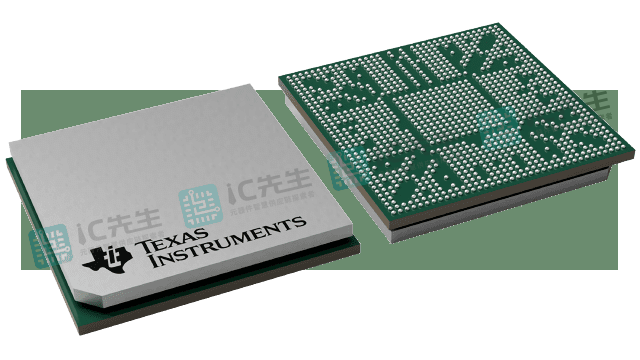

规格参数

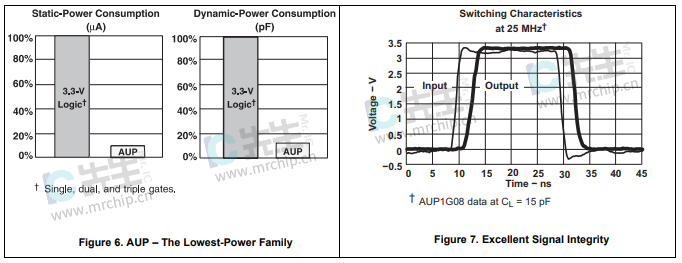

AUP系列是TI针对电池供电便携式设备行业低功耗需求的首要解决方案应用,该系列可确保整个VCC范围内的静态和动态功耗非常低因此电池寿命增加,该产品还保持了良好的信号完整性。它具有内置的少量滞后,允许较慢或有噪声的输入信号,降低的驱动器产生并防止输出上的过冲和下冲。

SN74AUP1G34DRLR型号驱动器产品功能:

0.8 V至3.6 V的宽工作VCC范围;

3.6V I/O容差,支持向下转换;

输入滞后允许缓慢的输入转换,并在输入端具有更好的开关噪声抗扰度;

当VCC为0 V时,Ioff功能允许输入和输出电压;

由于边缘速率较慢,噪声较低。

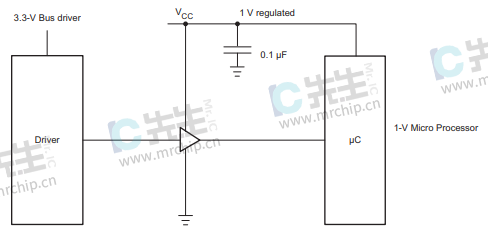

AUP系列的单门逻辑为新型低电压微处理器提供了出色的转换器,通常从0.8 V到1.2 V供电,它们可以降低外围驱动器和附件的电压,仍然由3.3V供电至新的uC功率水平。

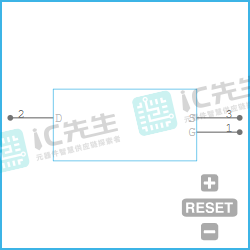

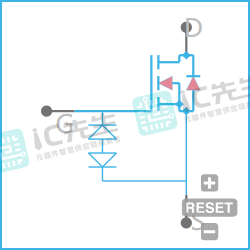

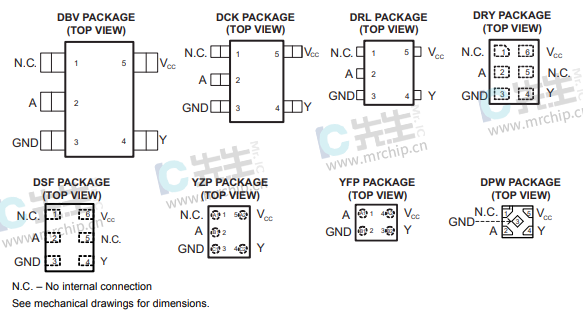

引脚功能图

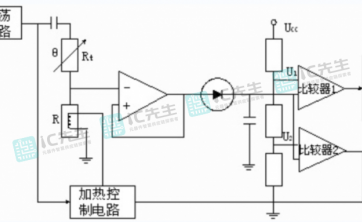

应用图

应用程序曲线

SN74AUP1G34DRLR型号器件采用CMOS技术,具有平衡输出驱动,应小心避开公共汽车竞争,因为它可以驱动超过最大限制的电流,当使用多位逻辑设备时,输入不应浮动。

在许多情况下,数字逻辑器件的功能或部分功能是未使用的,例如,当只有两个使用三输入AND门的输入,或者仅使用4个缓冲门中的3个,此类输入引脚不应保持未连接,因为外部连接处的未定义电压导致未定义的操作州。

所有未使用的数字输入逻辑器件必须连接到高或低偏置,以防止它们浮动,应该的逻辑级别应用于任何特定的未使用输入取决于设备的功能,通常情况下,它们将与GND或VCC,以更合理或更方便的为准。通常可以浮动输出,除非部分是收发器,如果收发器具有输出使能引脚,则当断言,这不会禁用IO的输入部分,因此禁用时它们也不能浮动。