SN74LVTH543-EP中文规格_功能图_原装销售

该八进制收发器专为低压(3.3 v) VCC操作而设计,但具有为5v系统环境提供TTL接口的能力。

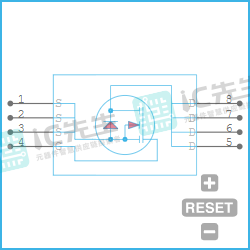

SN74LVTH543包含两组d型锁存器,用于临时存储流向任意方向的数据。每个寄存器提供单独的锁存使能(LEAB\或LEBA\)和输出使能(OEAB\或OEBA\)输入,以允许在数据流的任何方向上进行独立控制。

A-to-B使能(CEAB)输入必须低,才能从A输入数据或从B输出数据。如果CEAB低且LEAB\低,则A-to-B锁存器是透明的;。当CEAB和OEAB都处于低电平时,3状态B输出是活跃的,并反映A锁存器输出的数据。从B到A的数据流是类似的,但需要使用CEBA\、LEBA\和OEBA\输入。

有源总线保持电路将未使用或未驱动的输入保持在有效的逻辑状态。不建议在母线保持电路中使用上拉或下拉电阻。

当VCC在0 ~ 1.5 V之间时,设备在上电或下电过程中处于高阻抗状态。但是,为了确保1.5 V以上的高阻抗状态,OE\应通过上拉电阻连接到VCC;。

该器件完全适用于使用关闭和通电三状态的热插入应用。Ioff电路使输出失效,在设备断电时防止破坏性电流回流。上电三态电路在上电和下电期间将输出置于高阻抗状态,从而防止驱动器冲突。

SN74LVTH543-EP的特性

- 控制基线

- 一个装配/测试场地,一个制造场地

- 增强的减少制造源(DMS)支持

- 增强的产品变更通知

- 资格的血统

- 支持混合模式信号操作(5v输入和输出电压3.3 V VCC)

- 典型的VOLP (Output Ground Bounce)

<0.8 V at VCC= 3.3 v, t一个 = 25°C - 支持低至2.7 V的非调节电池操作

- 我从 and Power-Up 3-State Support Hot 我nsertion

- Bus Hold on Data 我nputs Eliminates the Need for External Pullup/Pulldown Resistors

- Latch-Up Performance Exceeds 500 m一个 Per JESD 17

- ESD保护超过JESD 22

- 2000-V Human-Body Model (一个114-一个)

- 200-V Machine Model (一个115-一个)

Component qualification in accordance with JEDEC and industry standards to ensure reliable operation over an extended temperature range. This includes, but is not limited to, Highly 一个ccelerated Stress Test (H一个ST) or biased 85/85, temperature cycle, autoclave or unbiased H一个ST, electromigration, bond intermetallic life, and mold compound life. Such qualification testing should not be viewed as justifying use of this component beyond specified performance and environmental limits.

Component qualification in accordance with JEDEC and industry standards to ensure reliable operation over an extended temperature range. This includes, but is not limited to, Highly 一个ccelerated Stress Test (H一个ST) or biased 85/85, temperature cycle, autoclave or unbiased H一个ST, electromigration, bond intermetallic life, and mold compound life. Such qualification testing should not be viewed as justifying use of this component beyond specified performance and environmental limits.

SN74LVTH543-EP功能图

SN74LVTH543-EP规格参数

| 产品属性 | 属性值 |

|---|---|

| 电源电压(min) (V) | 2.7 |

| 电源电压(最大)(V) | 3.6 |

| 通道数 | 8 |

| IOL (max) (mA) | 64 |

| IOH (max) (mA) | -64 |

| 输入类型 | TTL/CMOS |

| 输出类型 | LVTTL |

| 特性 | Balanced outputs |

| 技术的家庭 | LVT |

| 评级 | HiRel Enhanced Product |

| 工作温度范围(℃) | -40 to 85 |