SN74LVT573产品参数_产品特征_原装原厂

IC先生 网络 109 2023-12-04 17:31:30

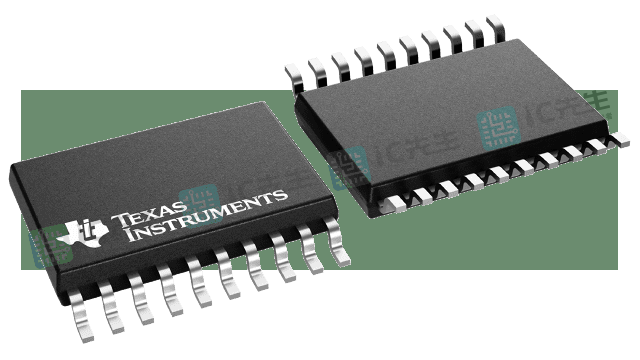

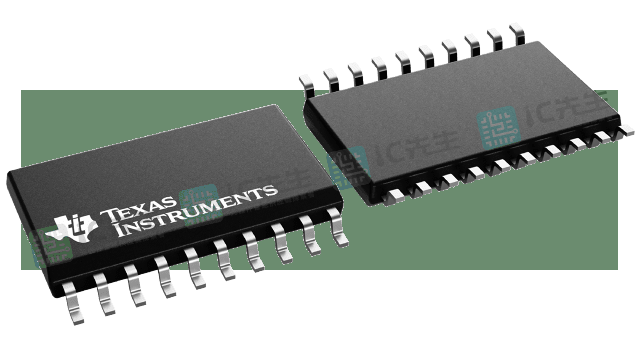

这些八进制锁存器专为低压(3.3 v) VCC操作而设计,但具有为5v系统环境提供TTL接口的能力。

LVT573的8个锁存器为透明d型锁存器。当锁存使能(LE)输入为高电平时,Q输出跟随数据(D)输入。当LE取低时,Q输出锁存在D输入处设置的逻辑电平上。

缓冲输出支持输入可用于将8个输出置于正常逻辑状态(高或低逻辑电平)或高阻抗状态。在高阻抗状态下,输出既不显著负载也不显著驱动母线。高阻抗状态和增加的驱动器提供了驱动总线线路的能力,而无需接口或上拉组件。不影响闭锁的内部操作。输出处于高阻抗状态时,可以保留旧数据,也可以输入新数据。

提供有源总线保持电路以将未使用的或浮动的数据输入保持在有效的逻辑电平。

为保证上电或下电时的高阻抗状态,应通过上拉电阻连接到VCC;。

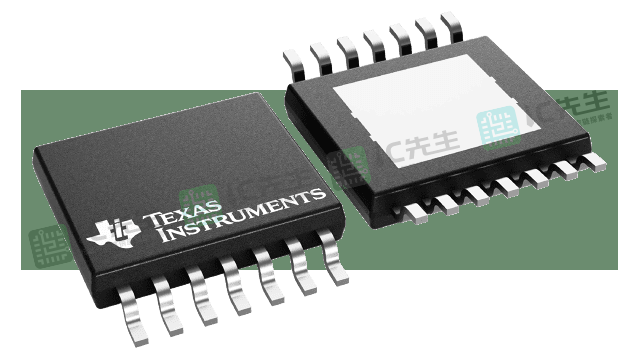

SN74LVT573采用TI的小型化小轮廓封装(DB),可在不到一半的印刷电路板面积内提供与标准小轮廓封装相同的I/O引脚数和功能。

SN54LVT573的特点是在-55°C至125°C的全军用温度范围内工作。SN74LVT573的特点是工作温度从-40°C到85°C。

SN74LVT573的特性

- 最先进的BiCMOS技术(一个BT)设计,3.3 v工作和低静态功耗

- 支持混合模式信号操作(5v输入输出电压3.3 V)CC)

- 支持低至2.7 V的非调节电池操作

- 典型的VOLP (Output Ground Bounce)< 0.8 V at VCC= 3.3 v, t一个 = 25°C

- ESD Protection Exceeds 2000 V Per MIL-STD-883C, Method 3015; Exceeds 200 V Using Machine Model (C = 200 pF, R = 0)

- Latch-Up Performance Exceeds 500 m一个 Per JEDEC Standard JESD-17

- 总线保持数据输入消除了外部上拉电阻的需要

- 支持实时插入

- Package Options Include Plastic Small-Outline (DW), Shrink Small-Outline (DB), and Thin Shrink Small-Outline (PW)Packages, Ceramic Chip Carriers (FK), Ceramic Flat (W)Packages, and Ceramic (J)DIPs

SN74LVT573功能图

SN74LVT573规格参数

| 产品属性 | 属性值 |

|---|---|

| 通道数 | 8 |

| 技术的家庭 | LVT |

| 电源电压(min) (V) | 2.7 |

| 电源电压(最大)(V) | 3.6 |

| 输入类型 | TTL-Compatible CMOS |

| 输出类型 | 3-State |

| 时钟频率(max) (MHz) | 160 |

| IOL (max) (mA) | 16 |

| IOH (max) (mA) | -16 |

| 电源电流(最大)(µA) | 5000 |

| 特性 | High speed (tpd 10-50ns) |

| 工作温度范围(℃) | -40 to 85 |

| 评级 | Catalog |

周度热榜

月度热榜

年度热榜

版权声明:

部分文章信息来源于网络以及网友投稿,本网站只负责对文章进行整理、排版、编辑,是出于传递更多信息之目的,并不意味着赞同其观点或证实其内容的真实性,如本站文章和转稿涉及版权等问题,请作者及时联系本站,我们会尽快处理。

文章标签:

芯片