STM32U599VJ中文参数_符号图_现货专卖

概述

STM32U59xxx器件属于基于高性能Arm的超低功耗微控制器系列(STM32U5系列)

®

皮质

®

-M33 32位RISC内核。

大脑皮层

®

-M33内核具有单精度FPU(浮点单元),支持所有Arm

®

单精度数据处理指令和所有数据类型。

大脑皮层

®

-M33核心还实现了一整套DSP(数字信号处理)指令和MPU(内存保护单元),增强了应用程序的安全性。

这些器件嵌入高速存储器(高达4兆字节的闪存和2.5兆字节的SRAM),用于静态存储器的FSMC(灵活的外部存储器控制器)(用于具有100引脚及以上封装的器件),两个Octo-SPI和一个十六进制spi存储器接口(所有封装上至少有一个Quad-SPI)以及广泛的增强型I/ o和外设连接到三个APB总线,三个AHB总线和32位多AHB总线矩阵。

设备提供符合Arm TBSA (trusted-based security architecture)要求的安全基础

®

.

该器件具有嵌入式闪存和SRAM的几种保护机制:读出保护,写保护,安全和隐藏保护区域。

这些设备嵌入了几个增强安全性的外围设备:一个HASH硬件加速器和一个真正的随机数生成器。

该设备提供主动篡改检测和保护,防止瞬态和环境扰动攻击,这要归功于几个内部监控,在攻击发生时生成秘密数据擦除。

该器件提供两个快速14位ADC (2.5 Msps),一个12位ADC (2.5 Msps),两个比较器,两个运算放大器,两个DAC通道,一个内部电压参考缓冲器,一个低功耗RTC,四个32位通用定时器,两个16位PWM定时器专用于电机控制,三个16位通用定时器,两个16位基本定时器和四个16位低功耗定时器。

这些设备提供了丰富的图形功能:用于快速纹理映射,缩放和旋转的Neo-Chrom GPU (GPU2D),用于平滑运动和透明效果的Chrom-ART (DMA2D),用于内存优化的Chrom-GRC (GFXMMU), MIPI

®

DSI主机控制器,具有两个DSI通道,每个通道运行速度高达500mbit /s,以及LCD-TFT控制器(LTDC)。

该器件支持MDF(多功能数字滤波器),具有六个专用于连接外部sigma-delta调制器的滤波器。

这些设备还具有标准和先进的通信接口,如:6i

2

c、3个spi、4个usart、2个UART和1个低功耗UART、2个sai、1个DCMI(数码相机接口)、2个sdmmc、1个FDCAN、1个USB OTG高速、1个USB Type-C™/USB Power Delivery控制器和1个通用同步8 /16位PSSI(并行数据输入/输出从接口)。

器件工作温度范围为-40 ~ +85℃(+ 105℃结)和-40 ~ +125℃(+130℃结),电源电压范围为1.71 ~ 3.6 V。

一套全面的节能模式允许低功耗应用的设计。

支持一些独立电源,如ADC、dac、opamp和比较器的模拟独立电源输入,USB的3.3 V专用电源输入和最多14个I/ o,可独立供电至1.08 V。

这些设备提供从64到216个引脚的10种封装。

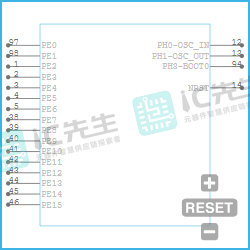

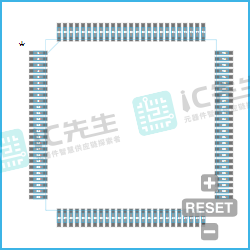

STM32U599VJ符号图

STM32U599VJ功能参数

- Includes ST state-of-the-art patented technology

- Ultra-low-power with FlexPowerControl

- 1.71 V to 3.6 V power supply

- - 40 °C to + 85/125 °C temperature range

- Low-power background autonomous mode (LPBAM): autonomous peripherals with DMA, functional down to Stop 2 mode

- VBAT mode: supply for RTC, 32 x 32-bit backup registers and 2-Kbyte backup SRAM

- 150 nA Shutdown mode (24 wake-up pins)

- 195 nA Standby mode (24 wake-up pins)

- 480 nA Standby mode with RTC

- 2 μA Stop 3 mode with 40-Kbyte SRAM

- 8.2 μA Stop 3 mode with 2.5-Mbyte SRAM

- 4.65 µA Stop 2 mode with 40-Kbyte SRAM

- 17.5 µA Stop 2 mode with 2.5-Mbyte SRAM

- 18.5 μA/MHz Run mode at 3.3 V

- 内核

- Arm® 32-bit Cortex®-M33 CPU with TrustZone®, MPU, DSP, and FPU

- ART Accelerator

- 32-Kbyte ICACHE allowing 0-wait-state execution from flash and external memories: frequency up to 160 MHz, 240 DMIPS

- 16-Kbyte DCACHE1 for external memories

- Power management

- Embedded regulator (LDO) and SMPS step-down converter supporting switch on-the-fly and voltage scaling

- Benchmarks

- 1.5 DMIPS/MHz (Drystone 2.1)

- 655 CoreMark® (4.09 CoreMark®/MHz)

- 369 ULPMark™-CP

- 89 ULPMark™-PP

- 47.2 ULPMark™-CM

- 120000 SecureMark™-TLS

- Memories

- Up to 4-Mbyte flash memory with ECC, 2 banks read-while-write, including 512 Kbytes with 100 kcycles

- With SRAM3 ECC off: 2514-Kbyte RAM including 66 Kbytes with ECC

- With SRAM3 ECC on: 2450-Kbyte RAM including 322 Kbytes with ECC

- External memory interface supporting SRAM, PSRAM, NOR, NAND, and FRAM memories

- 2 Octo-SPI memory interfaces

- 16-bit HSPI memory interface up to 160 MHz

- Rich graphic features

- Neo-Chrom GPU (GPU2D) accelerating any angle rotation, scaling, and perspective correct texture mapping

- 16-Kbyte DCACHE2

- Chrom-ART Accelerator (DMA2D) for smooth motion and transparency effects

- Chrom-GRC (GFXMMU) allowing up to 20 % of graphic resources optimization

- MIPI® DSI host controller with two DSI lanes running at up to 500 Mbit/s each

- LCD-TFT controller (LTDC)

- Digital camera interface

- General-purpose input/outputs

- Up to 156 fast I/Os with interrupt capability most 5V-tolerant and up to 14 I/Os with independent supply down to 1.08 V

- Clock management

- 4 to 50 MHz crystal oscillator

- 32 kHz crystal oscillator for RTC (LSE)

- Internal 16 MHz factory-trimmed RC (± 1 %)

- Internal low-power 32 kHz RC (± 5 %)

- 2 internal multispeed 100 kHz to 48 MHz oscillators, including one autotrimmed by LSE (better than ±0.25 % accuracy)

- Internal 48 MHz

- 5 PLLs for system clock, USB, audio, ADC, DSI

- 安保

- Arm® TrustZone® and securable I/Os, memories, and peripherals

- Flexible life cycle scheme with RDP and password-protected debug

- Root of trust thanks to unique boot entry and secure hide-protection area (HDP)

- Secure firmware installation (SFI) thanks to embedded root secure services (RSS)

- Secure firmware upgrade support with TF-M

- HASH hardware accelerator

- True random number generator, NIST SP800-90B compliant

- 96-bit unique ID

- 512-byte OTP (one-time programmable)

- Active tampers

- Up to 17 timers, 2 watchdogs and RTC

- 19 timers: 2 16-bit advanced motor-control, 4 32-bit, 3 16-bit general purpose, 2 16-bit basic, 4 low-power 16-bit (available in Stop mode), 2 SysTick timers, and 2 watchdogs

- RTC with hardware calendar, alarms, and calibration

- Up to 25 communication peripherals

- 1 USB Type-C®/USB power delivery controller

- 1 USB OTG high-speed with embedded PHY

- 2 SAIs (serial audio interface)

- 6 I2C FM+(1 Mbit/s), SMBus/PMBus™

- 7 USARTs (ISO 7816, LIN, IrDA, modem)

- 3 SPIs (6x SPIs with OCTOSPI/HSPI)

- 1 CAN FD controller

- 2 SDMMC interfaces

- 1 multifunction digital filter (6 filters) + 1 audio digital filter with sound-activity detection

- Parallel synchronous slave interface

- Mathematical coprocessor

- CORDIC for trigonometric functions acceleration

- FMAC (filter mathematical accelerator)

- Rich analog peripherals (independent supply)

- 2 14-bit ADC 2.5-Msps with hardware oversampling

- 1 12-bit ADC 2.5-Msps, with hardware oversampling, autonomous in Stop 2 mode

- 12-bit DAC (2 channels), low-power sample, and hold, autonomous in Stop 2 mode

- 2 operational amplifiers with built-in PGA

- 2 ultra-low-power comparators

- ECOPACK2 compliant packages

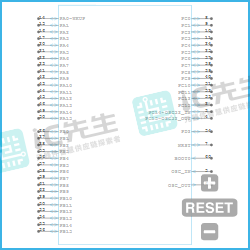

STM32U599VJ引脚图

STM32U599VJ 3D图