STM32H7A3LI规格参数_功能图_原厂出售

IC先生 网络 40 2023-12-21 17:10:18

概述

STM32H7A3xI/G器件基于高性能Arm

®

皮质

®

-M7 32位RISC内核,工作频率高达280mhz。

®

-M7内核具有支持Arm的浮点单元(FPU)

®

双精度(IEEE 754兼容)和单精度数据处理指令和数据类型。

STM32H7A3xI/G器件采用高速嵌入式存储器,具有高达2mb的双银行闪存,约1.4 mb的RAM(包括192kb的TCM RAM, 1.18 mb的用户SRAM和4kb的备份SRAM),以及广泛的增强型I/ o和外设,连接到四个APB总线,三个AHB总线,32位多AHB总线矩阵和支持内部和外部存储器访问的多层AXI互连。

所有器件提供两个adc,两个DAC(一个双DAC和一个单DAC),两个超低功耗比较器,一个低功耗RTC, 12个通用16位定时器,两个用于电机控制的PWM定时器,三个低功耗定时器,一个真正的随机数发生器(RNG)。

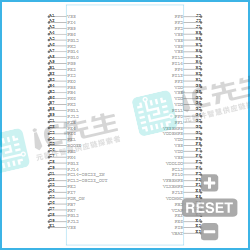

STM32H7A3LI符号图

STM32H7A3LI功能参数

- 内核

- 32-bit Arm® Cortex®-M7 core with double-precision FPU and L1 cache: 16 Kbytes of data and 16 Kbytes of instruction cache allowing to fill one cache line in a single access from the 128-bit embedded Flash memory; frequency up to 280 MHz, MPU, 599 DMIPS/ 2.14 DMIPS/MHz (Dhrystone 2.1), and DSP instructions

- Memories

- Up to 2 Mbytes of Flash memory with read while write support, plus 1 Kbyte of OTP

- ~1.4 Mbytes of RAM: 192 Kbytes of TCM RAM (inc. 64 Kbytes of ITCM RAM + 128 Kbytes of DTCM RAM for time critical routines), 1.18 Mbytes of user SRAM, and 4 Kbytes of SRAM in Backup domain

- 2x Octo-SPI memory interfaces with on-the-fly decryption, I/O multiplexing and support for serial PSRAM/NOR, Hyper RAM/Flash frame formats, running up to 140 MHz in SRD mode and up to 110 MHz in DTR mode

- Flexible external memory controller with up to 32-bit data bus:

- SRAM, PSRAM, NOR Flash memory clocked up to 125 MHz in Synchronous mode

- SDRAM/LPSDR SDRAM,

- 8/16-bit NAND Flash memory

- CRC calculation unit

- 安保

- ROP, PC-ROP, active tamper, secure firmware upgrade support

- General-purpose input/outputs

- Up to 168 I/O ports with interrupt capability

- Fast I/Os capable of up to 133 MHz

- Up to 164 5 V-tolerant I/Os

- Up to 168 I/O ports with interrupt capability

- Low-power consumption

- Stop: down to 32 µA with full RAM retention

- Standby: 2.8 µA (Backup SRAM OFF, RTC/LSE ON, PDR OFF)

- VBAT: 0.8 µA with RTC and LSE ON

- Clock management

- Internal oscillators: 64 MHz HSI, 48 MHz RC, 4 MHz CSI, 32 kHz LSI

- External oscillators: 4-50 MHz HSE, 32.768 kHz LSE

- 3× PLLs (1 for the system clock, 2 for kernel clocks) with fractional mode

- Reset and power management

- 2 separate power domains, which can be independently clock gated to maximize power efficiency:

- CPU domain (CD) for Arm® Cortex® core and its peripherals , which can be independently switched in Retention mode

- mart run domain (SRD) for reset and clock control, power management and some peripherals

- 1.62 to 3.6 V application supply and I/Os

- POR, PDR, PVD and BOR

- Dedicated USB power embedding a 3.3 V internal regulator to supply the internal PHYs

- Dedicated MMC power supply

- High power efficiency SMPS step-down converter regulator to directly supply VCORE or an external circuitry

- Embedded regulator (LDO) with configurable scalable output to supply the digital circuitry

- Voltage scaling in Run and Stop mode

- Backup regulator (~0.9 V)

- Low-power modes: Sleep, Stop and Standby

- VBAT battery operating mode with charging capability

- CPU and domain power state monitoring pins

- 2 separate power domains, which can be independently clock gated to maximize power efficiency:

- Interconnect matrix

- 5 DMA controllers to unload the CPU

- 1× high-speed general-purpose master direct memory access controller (MDMA)

- 2× dual-port DMAs with FIFO and request router capabilities

- 1× basic DMA with request router capabilities

- 1x basic DMA dedicated to DFSDM

- Up to 35 communication peripherals

- 4× I2C FM+ interfaces (SMBus/PMBus)

- 5× USART/5x UARTs (ISO7816 interface, LIN, IrDA, modem control) and 1x LPUART

- 6× SPIs, including 4 with muxed full-duplex I2S audio class accuracy via internal audio PLL or external clock and 1 x SPI/I2S in LP domain (up to 125 MHz)

- 2x SAIs (serial audio interface)

- SPDIFRX interface

- SWPMI single-wire protocol master I/F

- MDIO Slave interface

- 2× SD/SDIO/MMC interfaces (up to 133 MHz)

- 2× CAN controllers: 2 with CAN FD, 1 with time-triggered CAN (TT-CAN)

- 1× USB OTG interfaces (1HS/FS)

- HDMI-CEC

- 8- to 14-bit camera interface up to 80 MHz

- 8-/16-bit parallel synchronous data input/output slave interface (PSSI)

- 11 analog peripherals

- 2× ADCs with 16-bit max. resolution (up to 24 channels, up to 3.6 MSPS)

- 1× analog and 1x digital temperature sensors

- 1× 12-bit single-channel DAC (in SRD domain) + 1× 12-bit dual-channel DAC

- 2× ultra-low-power comparators

- 2× operational amplifiers (8 MHz bandwidth)

- 2× digital filters for sigma delta modulator (DFSDM), 1x with 8 channels/8 filters and 1x in SRD domain with 2 channels/1 filter

- Graphics

- LCD-TFT controller up to XGA resolution

- Chrom-ART graphical hardware Accelerator (DMA2D) to reduce CPU load

- Hardware JPEG Codec

- Chrom-GRC™ (GFXMMU)

- Up to 19 timers and 2 watchdogs

- 2× 32-bit timers with up to 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder input (up to 280 MHz)

- 2× 16-bit advanced motor control timers (up to 280 MHz)

- 10× 16-bit general-purpose timers (up to 280 MHz)

- 3× 16-bit low-power timers (up to 280 MHz)

- 2× watchdogs (independent and window)

- 1× SysTick timer

- RTC with sub-second accuracy and hardware calendar

- Debug mode

- SWD & JTAG interfaces

- 4 Kbytes Embedded Trace Buffer

- 1x 32-bit, NIST SP 800-90B compliant, true random generator

- 96-bit unique ID

- All packages are ECOPACK2 compliant

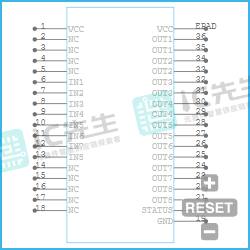

STM32H7A3LI引脚图

STM32H7A3LI 3D图

周度热榜

月度热榜

年度热榜

版权声明:

部分文章信息来源于网络以及网友投稿,本网站只负责对文章进行整理、排版、编辑,是出于传递更多信息之目的,并不意味着赞同其观点或证实其内容的真实性,如本站文章和转稿涉及版权等问题,请作者及时联系本站,我们会尽快处理。

文章标签:

芯片