AM6526产品规格_功能图_现货出售

AM654x 和 AM652x Sitara™ 处理器是 Arm 应用处理器,旨在满足现代工业 4.0 嵌入式产品的复杂处理需求。

AM654x 和 AM652x 器件将四个或两个 Arm Cortex-A53 内核与双 Arm Cortex-R5F MCU 子系统(包括旨在帮助客户实现其最终产品功能安全目标的特性)和三个千兆位工业通信子系统 (PRU_ICSSG) 组合在一起,从而为功能安全应用实现支持 SoC 且具有工业连接和处理能力的高性能工业控制。 AM65xx 目前正在按照 IEC 61508 标准要求,接受 TÜV SÜD 的认证评估。

AM654x 中的四个 Arm Cortex-A53 内核分布在两个具有共享 L2 存储器的双核集群中,以创建两个处理通道。 AM652x 中的两个 Arm Cortex-A53 内核可通过单个双核集群和两个单核集群选项提供。片上存储器、外设和互联中包含广泛的 ECC,可确保可靠性。整个 SoC 中包括旨在帮助客户设计可实现他们的功能安全目标的特性(正在等待 TÜV SÜD 评估结果)。除了 DMSC 管理的粒度防火墙之外,某些 AM654x 和 AM652x 器件上还提供了加密加速和安全启动功能。

Arm Cortex-A53 RISC CPU 及 Arm Neon™ 扩展可实现可编程性,而双 Arm Cortex-R5F MCU 子系统可作为两个内核用于一般用途或用于锁步模式,以帮助满足功能安全应用的需求。PRU_ICSSG 子系统可用于提供最多六个工业以太网端口,如 Profinet IRT、TSN、Ethernet/IP 或 EtherCAT 等,或者用于标准千兆位以太网连接。

TI 提供了一整套针对 Arm 内核的软件和开发工具,其中包括 Processor SDK Linux、Linux-RT、RTOS 和 Android 以及 C 语言编译器和一个可查看源代码执行情况的调试界面。我们将会提供相关功能安全和安保文档,以帮助客户开发功能安全或安保相关的系统。

AM6526的特性

处理器内核:

- 双核或四核 Arm Cortex-A53 微处理器子系统(高达 1.1GHz)

- 最多两个双核或两个单核 Arm Cortex-A53 集群(具有 512KB L2 缓存,包括 SECDED)

- 每个 A53 内核具有 32KB L1 指令缓存和 32K L1 数据缓存

- 双核 Arm Cortex-R5F(高达 400MHz)

- 支持锁步模式

- 每个 R5F 内核具有 16KB 指令缓存、16KB 数据缓存和 64KB RAM

工业子系统:

- 三个千兆位工业通信子系统 (PRU_ICSSG)

- 每个 PRU_ICSSG 具有最多两个 10/100/1000 以太网端口

- 支持两个 SGMII 端口(2)

- 与 10/100Mb PRU-ICSS 兼容

- 每个 PRU_ICSSG 具有 24 个 PWM

- 逐周期控制

- 增强跳闸控制

- 每个 PRU_ICSSG 具有 18 个 Σ-Δ 滤波器

- 短路逻辑

- 过流逻辑

- 每个 PRU_ICSSG 具有 6 个多协议位置编码器接口

存储器子系统:

- 高达 2MB 的片上 L3 RAM(具有 SECDED)

- 多核共享存储器控制器 (MSMC)

- 高达 2MB(2 组 × 1MB)的 SRAM(具有 SECDED)

- 共享相干 2 级或 3 级存储器映射 SRAM

- 共享相干 3 级缓存

- 256 位处理器端口总线和 40 位物理地址总线

- 用于连接处理器或设备主机的相干统一双向接口

- L2、L3 缓存预热和后清除

- 具有饥饿限制的带宽管理

- 一个基础设置主接口

- 单个外部存储器主接口

- 支持分布式虚拟系统

- 支持内部 DMA 引擎 - 数据路由单元 (DRU)

- ECC 错误保护

- 高达 2MB(2 组 × 1MB)的 SRAM(具有 SECDED)

- DDR 子系统 (DDRSS)

- 支持高达 DDR-1600 的 DDR4 存储器类型

- 32 位数据总线和 7 位 SECDED 总线

- 8 GB 全部可寻址空间

- 通用存储器控制器 (GPMC)

SafeTI™ 半导体组件:

- 专为功能安全应用而设计

- 根据 IEC 61508 标准的要求开发

- 达到 SIL-3 的系统完整性

- 对于 MCU 安全岛,包含足够的诊断以达到 SIL-2 的随机故障完整性要求

- 对于 SoC 的其余部分,包含足够的诊断以达到 SIL-2 的随机故障完整性要求

- 此外,还需要配置足够的架构指标,以实现考虑特定安全概念的 SIL-3 的执行(如软件互惠式比较)

- 提供功能安全手册

- 安全相关认证

- TÜV SÜD 组件级功能安全认证 [正在认证]

- 功能安全特性:

- 计算临界存储器的 ECC 或奇偶校验和内部总线互联

- 有助于防止干扰 (FFI) 的防火墙

- 适用于 CPU、高端计时器和片上 RAM 的内置自检 (BIST)

- 针对诊断测试的硬件错误注入支持

- 用于捕获功能安全相关错误的错误信号模块 (ESM)

- 电压、温度和时钟监控

- 多个时钟域内的窗口式和非窗口式看门狗计时器

- MCU 岛

- 隔离了双核 Arm Cortex-R5F 微处理器子系统,

- 独立的电压、时钟、复位和专用外设

- 与 SoC 其余部分的内部 MCSPI 连接

安全:

- 支持安全启动

- 硬件强制可信根

- 支持通过备用秘钥转换可信根

- 支持接管保护、IP 保护和防回滚保护

- 支持加密加速

- 会话感知型加密引擎可基于输入数据流自动切换密钥材料

- 支持加密内核

- AES – 128/192/256 位秘钥大小

- 3DES – 56/112/168 位秘钥大小

- MD5、SHA1

- SHA2 – 224/256/384/512

- 具有真随机数生成器的 DRBG

- 可在 RSA/ECC 处理中提供帮助的 PKA(公钥加速器)

- DMA 支持

- 调试安全性

- 安全软件控制的调试访问

- 安全感知调试

- 支持可信执行环境 (TEE)

- 基于 Arm TrustZone 的 TEE

- 可实现隔离的广泛防火墙支持

- 安全 DMA 路径和互联

- 安全监视器/计时器/IPC

- 安全存储支持

- OSPI 接口实时加密和实时认证支持

- 通过基于数据包的硬件加密引擎为数据(有效载荷)加密/认证提供网络安全支持

- 用于密钥和安全管理的安全协处理器 (DMSC),具有用于安全软件的专用设备级互连

SoC 服务:

- 设备管理安全控制器 (DMSC)

- 集中式 SoC 系统控制器

- 管理系统服务,包括初始引导、安保、功能安全和时钟/复位/电源管理

- 支持激活和低功耗模式的电源管理控制器

- 通过消息管理器与各种处理单元通信

- 简化的接口可优化未使用的外设

- 跟踪和调试功能

- 十六个 32 位通用计时器

- 两个数据移动和控制导航器子系统 (NAVSS)

- 环形加速器 (RA)

- 统一 DMA (UDMA)

- 最多 2 个计时器管理器 (TM)(每个负责 1024 个计时器)

多媒体:

- 显示子系统

- 与两个显示输出相关联的两个完全输入映射覆盖管理器

- 一个端口 MIPI DPI 并行接口

- 1 个 OLDI 端口

- PowerVR SGX544-MP1 3D 图形处理单元 (GPU)

- 一个摄像头串行接口 2 (MIPI CSI-2)

- 一个端口视频捕捉:BT.656/1120(没有嵌入式同步)

高速接口:

- 支持一个千兆位以太网 (CPSW) 接口

- RMII (10/100) 或 RGMII (10/100/1000)

- IEEE1588(2008 附件 D、E 和 F)及 802.1AS PTP

- 音频/视频桥接 (P802.1Qav/D6.0)

- 节能以太网 (802.3az)

- 巨型帧(2024 字节)

- 第 45 条 MDIO PHY 管理规范

- 两个 PCI-Express (PCIe) 修订版 3.1 子系统(2)

- 支持 第二代 (5.0GT/s) 运行

- 两个独立的单通道端口或一个双通道端口

- 支持并发根复合体和端点运行

- USB 3.1 双角色设备 (DRD) 子系统(2)

- 一个增强型超速第一代端口

- 一个 USB 2.0 端口

- 每个端口均可独立配置为 USB 主机、USB 外设或 USB DRD

通用连接:

- 6 个内部集成电路 (I2C™) 端口

- 5 个可配置 UART/IrDA/CIR 模块

- 2 个同步闪存接口,配置为

- 两个 OSPI 闪存接口

- 或 HyperBus™ 和 OSPI1 闪存接口

- 2 个 12 位模数转换器 (ADC)

- 最高每秒 400 万个样本

- 八个多路复用模拟输入

- 8 个多通道串行外设接口 (MCSPI) 控制器

- 两个具有内部连接

- 六个具有外部接口

- 通用 I/O (GPIO) 引脚

控制接口:

- 6 个增强型高分辨率脉宽调制器 (EHRPWM) 模块

- 一个增强型捕捉 (ECAP) 模块

- 3 个增强型正交编码器脉冲 (EQEP) 模块

汽车接口:

- 2 个模块化控制器区域网 (MCAN) 模块,具有完整 CAN-FD 支持

音频接口:

- 3 个多通道音频串行端口 (MCASP) 模块

媒体和数据存储:

- 2 个多媒体卡™/安全数字 (MMC™/SD) 接口

简化的电源管理:

- 完全支持双电压 I/O 的简化电源序列

- 集成的 LDO 可降低电源解决方案的复杂性

- 集成的 SDIO LDO 可为 SD 接口处理自动电压转换

- 集成了上电复位 (POR) 发生功能,可降低电源解决方案的复杂性

- 集成了电压监控器,可实现功能安全监控

- 集成了电源干扰检测器,可检测快速电源瞬变

模拟/系统集成:

- 集成了 USB VBUS 检测

- 针对 DDR 复位的失效防护 I/O

- 复位期间禁用所有 I/O 引脚驱动器,以防止总线冲突

- 复位期间禁用默认 I/O 牵引功能,以防止系统冲突

- 支持动态 I/O Pinmux 配置更改

片上系统 (SoC) 架构:

- 支持从 UART、I2C、OSPI、HyperBus、并行 NOR 闪存、SD 或 eMMC™、USB、PCIe 和以太网接口的主引导

- 28nm CMOS 技术

- 23mm × 23mm、0.8mm 间距、784 引脚 FCBGA (ACD)

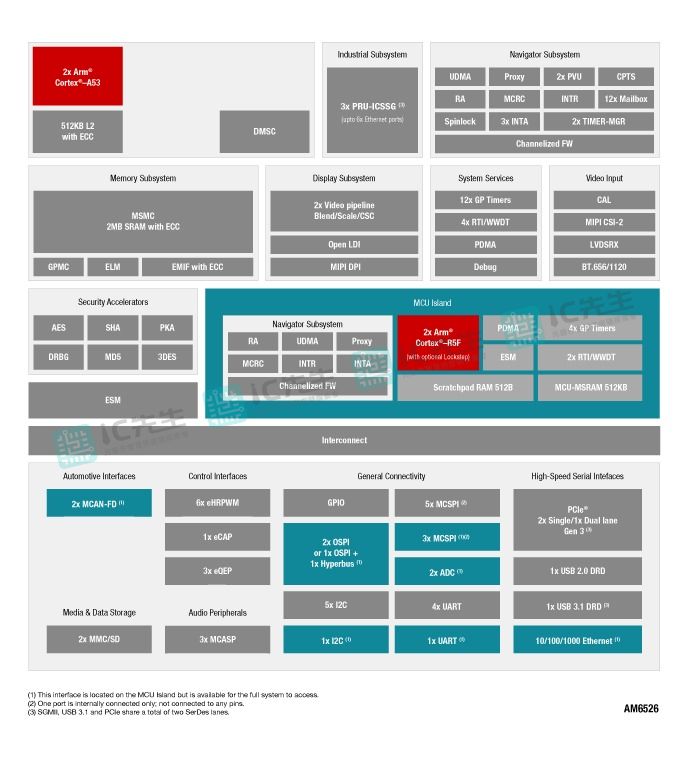

AM6526功能图

AM6526规格参数

| 产品属性 | 属性值 |

|---|---|

| Arm处理器 | 2 Arm Cortex-A53 |

| 臂(最大)(MHz) | 1100 |

| 协处理器 | 2 Arm Cortex-R5F |

| CPU | 64-bit |

| 显示类型 | MIPI DPI, OLDI |

| 协议 | EtherCAT, Ethernet, ICSS, Profibus, Profinet, TSN |

| 以太网MAC | 1-Port 10/100/1000, 6-Port 10/100/1000 PRU EMAC |

| 作为PCIe | 2 PCIe Gen 3 |

| 特性 | Networking |

| 操作系统 | Android, Linux, RTOS |

| 安全 | Cryptography, Debug security, Device identity, Isolation firewalls, Secure boot, Secure storage & programming, Software IP protection |

| TI功能安全类别 | Functional Safety-Compliant |

| 评级 | Catalog |

| 电源解决方案 | TPS6594-Q1 |

| 工作温度范围(℃) | -40 to 105 |