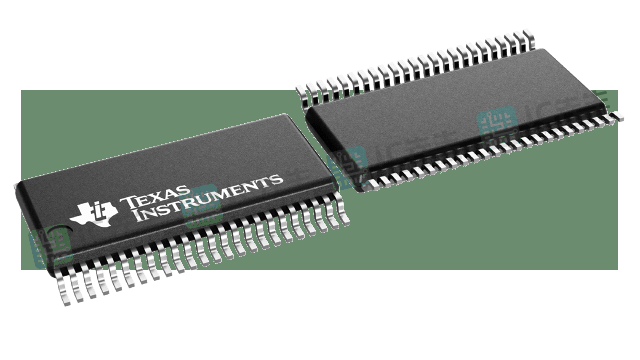

DS92LX1621中文参数_功能图_原装供应

IC先生 网络 97 2023-11-03 08:28:34

DS92LX1621 / DS92LX1622芯片组提供了一个通道Link III接口,具有高速前向通道和全双工后向通道,通过单个差分对进行数据传输。序列化器/反序列化器对用于汽车摄像头系统与主控制器/电子控制单元(ECU)之间的直接连接。。包含16位有效负载的是CRC(循环冗余校验)或奇偶校验位的可选数据完整性选项,以监控传输链路错误。使用TI的嵌入式时钟技术允许在单个差分对上进行透明的全双工通信,携带不对称的双向控制信息,而不依赖于视频消隐间隔。这种单串行流通过消除并行数据和时钟路径之间的倾斜问题,简化了在PCB走线和电缆上传输宽数据总线。这大大节省了系统成本,通过缩小数据路径,从而减少PCB层,电缆宽度,连接器尺寸和引脚。

此外,反序列化器输入提供均衡控制,以补偿介质在较长距离上的损失。采用内部直流平衡编码/解码,支持交流耦合互连。

休眠功能为远端设备的信令提供了一种省电模式和远程唤醒中断。

序列化器提供32针WQFN封装,反序列化器提供40针WQFN封装。

DS92LX1621的特性

- 可配置数据吞吐量

- 12–bit (min) up to 600 Mbits/sec

- 16–bit (def) up to 800 Mbits/sec

- 18–bit (max) up to 900 Mbits/sec

- 支持10mhz ~ 50mhz输入时钟

- 嵌入式时钟与DC均衡编码

支持交流耦合互连 - 能够驾驶高达10米的屏蔽

双绞 - 双向控制接口通道

我2C支持 - 我2C 我nterface for Device

Configuration. Single-pin 我D Addressing - 16–bit Data Payload with CRC (Cyclic

Redundancy Check) for Checking Data 我ntegrity

可编程数据传输错误

Detection and 我nterrupt Control - Up to 6 Programmable GP我O’s

- AT-SPEED B我ST Diagnosis Feature to Validate

Link 我ntegrity - 我ndividual Power-Down Controls for Both SER

和DES - 用户可选择并行数据的时钟边缘

on Both SER 和DES - 我ntegrated Termination Resistors

- 1.8V- or 3.3V-Compatible Parallel Bus 我nterface

- 单电源1.8V

- 我EC 61000–4–2 ESD Compliant

- 反序列化器不需要参考时钟

- 可编程接收均衡

- 锁输出报告引脚,以确保链路

状态 - EM我/EMC Mitigation

- DES可编程扩频(SSCG)

输出 - DES Receiver Staggered 输出

- DES可编程扩频(SSCG)

- Temperature Range −40°C to +85°C

- SER Package: 32 Pin WQFN (5mm × 5mm)

- DES Package: 40 Pin WQFN (6mm × 6mm)

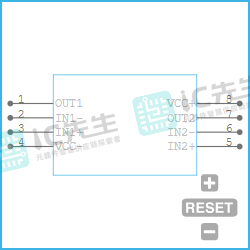

DS92LX1621功能图

DS92LX1621规格参数

| 产品属性 | 属性值 |

|---|---|

| 协议 | Catalog |

| 评级 | Catalog |

| 工作温度范围(℃) | -40 to 85 |

周度热榜

月度热榜

年度热榜

版权声明:

部分文章信息来源于网络以及网友投稿,本网站只负责对文章进行整理、排版、编辑,是出于传递更多信息之目的,并不意味着赞同其观点或证实其内容的真实性,如本站文章和转稿涉及版权等问题,请作者及时联系本站,我们会尽快处理。

文章标签:

芯片