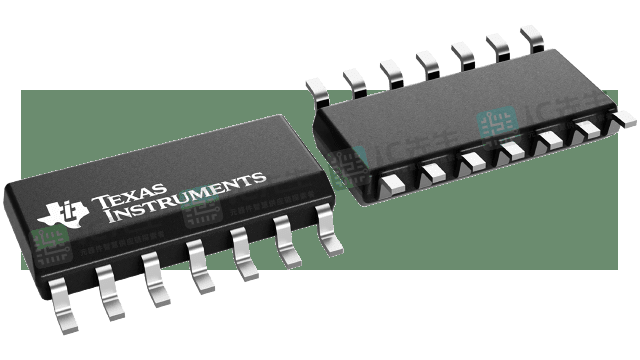

SN75LVDS86产品参数_功能图_原厂出售

IC先生 网络 170 2023-11-07 14:08:24

SN75LVDS86 FlatLink接收器在单个集成电路中包含三个串行输入7位并行输出移位寄存器,一个7x时钟合成器和四个低压差分信号(LVDS)线接收器。这些功能允许从兼容的发射器接收同步数据,例如SN75LVDS81, '83, '84或'85,通过四个平衡对导体,并以较低的传输速率扩展到21位单端低压TTL (LVTTL)同步数据。。

当接收时,高速LVDS数据被接收并以7倍的LVDS输入时钟(CLKIN)速率加载到寄存器中。然后数据以CLKIN速率卸载到21位宽LVTTL并行总线。锁相环路时钟合成器电路产生一个用于内部时钟的7x时钟和一个用于扩展数据的输出时钟。SN75LVDS86在输出时钟的下降沿(CLKOUT)上呈现有效数据。。

SN75LVDS86只需要四个线端电阻用于差分输入,很少或没有控制。数据总线在发射器的输入和接收器的输出处显示相同,数据传输对用户是透明的。。该信号的低电平清除所有内部寄存器到低电平。

SN75LVDS86的LVDS接收器包括开路故障安全设计,当输入未连接到LVDS驱动器时,接收器输出转到低电平。即使线路在接收器输入端差分终止,也会发生这种情况。

SN75LVDS86的特点是可在0°C至70°C的环境自由空气温度下工作。

SN75LVDS86的特性

- 3:21数据通道扩展,吞吐量可达178.5 mb /s

- 适用于SVGA, XGA,或SXGA显示数据传输从控制器显示极低的电磁干扰

- 3个数据通道和时钟低压差分通道输入和21个数据和时钟低压TTL通道输出

- 从单个3.3 v电源和250 mW(类型)运行

- 5 v宽容SHTDN输入

- 母线引脚ESD保护超过4kv

- 封装在薄收缩小轮廓包装(TSSOP)与20-Mil端子间距

- 禁用时消耗小于1mw

- Wide Phase-Lock输入 Frequency Range 31 MHz to 68 MHz

- 锁相环不需要外部元件

- 开路接收机故障安全设计

- 输入满足或超过ANSI EIA/TIA-644标准的要求

- Improved Replacement for the National™ DS90C562

FlatLink是德州仪器的商标。

所有其他商标均为其各自所有者的财产。

SN75LVDS86功能图

SN75LVDS86规格参数

| 产品属性 | 属性值 |

|---|---|

| 协议 | Catalog |

| 评级 | Catalog |

| 工作温度范围(℃) | 0 to 70 |

周度热榜

月度热榜

年度热榜

版权声明:

部分文章信息来源于网络以及网友投稿,本网站只负责对文章进行整理、排版、编辑,是出于传递更多信息之目的,并不意味着赞同其观点或证实其内容的真实性,如本站文章和转稿涉及版权等问题,请作者及时联系本站,我们会尽快处理。

文章标签:

芯片